Multisim仿真文件和word版文档

基于multisim的多功能数字钟仿真.zip

(750.81 KB, 售价: 3 E币)

基于multisim的多功能数字钟仿真.zip

(750.81 KB, 售价: 3 E币)

仿真原理图如下(Multisim仿真工程文件和word版文档可到本帖附件中下载)

1、画出数字电子钟的结构框图。

2、设计一个输出电压为5V的直流稳压电源。

3、用555或其它电路产生一个秒脉冲发生器。

4、用74160设计时分秒计数器,通过开关可实现二十四与十二进制计 数值的转换。

5、有译码实现电路,具有校时、校分的功能,可以对时和分单独校时。

6、蜂鸣器整点报时。

主要任务(需附有技术指标分析):

(1)设计制作一个可容纳8组参赛的数字式抢答器,每组设置一个抢答按钮供抢答者使用。

(2)电路具有第一抢答信号的鉴别和锁存功能。在主持人系统发出抢答指令后,若参赛者按抢答开关,则该组指示灯亮并用组别显示电路显示出抢答者的组别,同时指示灯(发光二极管)亮。此时,电路应具备自锁存功能,使别组的抢答开关不起作用。

(3)若超时仍无人抢答,则报警指示灯熄灭。

1 通过此次数字钟的设计,学习、了解、掌握、常用电子电路设计的思路与过程。 2 了解到怎样用MULTISIM这个软件绘制并仿真电路原理图,培养学生运用现代化工具完成各种各样电子电路及系统设计。 3 加强应用新技术、新方法、新器件的训练。强化工程能力和创新能力的培养。 4 将理论知识与实际相结合,避免培养纸上谈兵的学生。 5 学习掌握电路一般的设计方法,了解到电子产品研制开发过程。 6 提高电子电路实验技能及仪器使用能力。 7 掌握电子电路安装和调试的方法及故障排除方法。 8 通过查阅资料和文献资料,培养同学们独立发现、解决问题的意识与能力。 9 培养创新能力和创新思维,培养应用所学知识指导实践的能力,同时掌握数字电路的基本原理知识。

1.2 实验要求 (1) 设计该课题所需的六十进制、二十四进制。 (2) 设计数码管译码显示电路。 (3) 设计秒与分、分与时之间的进位控制电路。 (4) 设计整点提醒电路。 (5) 设计手动校时电路。

2 电路总体设计

设计框图:

总体原理说明: 整体电路共分为五大模块: 脉冲产生模块、 计时模块、译码显示模块、 整点报时模块、 校时模块。 主要由555定时器器、秒计数器、分计数器、时计数器、 BCD-七段显示译码 / 驱动器、 LED七段显示数码管、时间校准电路构成以及各种门电路。 数字钟数字译码显示部分,采用共阴译码器与共阴极数码管串联电路,将译码器、 七段数码管连接起来之间串个组排,组成十进制数码显示电路, 即时钟显示。要完成显示需要 6 个数码管, 八段的数码管需要译码器将计数信号译码成BCD码才能显示,然后要实现时、分、秒的计时需要 60 进 制计数器和 24 进制计数器,脉冲发生电路则有555定时器构成的多谐振荡电路。 60 进制则由 10进制和 6 进制的计数器串联而成,。 计数器的输出分别经译码器送显示器显示。 计时出现误差时,可以用校时电路校 时、校分。校时电路由复位按钮构成,复位按钮按下产生手动脉冲,从而调节计数器,实现校时。 整点报时电路则有门电路构成的判断模块对时计时和分计时的输出进行判断,从而实现整点报时。

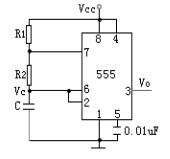

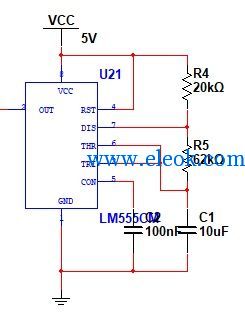

3各部分电路设计 3.1 脉冲产生模块设计 脉冲发生电路采用555构成的多谐振荡电路。

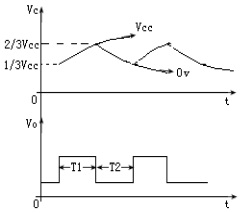

用 555 定时器构成的多谐振荡器电路如图所示:图中电容 C、电阻 R1 和 R2 作 为振荡器的定时元件,决定着输出矩形波正、负脉冲的宽度。定时器的触发输入端(2脚)和阀 值输入端(6 脚)与电容相连;集电极开路输出端(7脚)接 R1、R2 相连处,用以控制电容 C 的充、放电;外界控制输入端(5脚)通过 0.01uF 电容接地。

多谐振荡器的工作波形如图 6-11(b) 所示:电路接通电源的瞬间,由于电容 C 来不及充电, Vc=0v ,所以 555 定时器状态为 1,输出 Vo 为高电平。同时,集电极输出端(7 脚)对地断开,电源 Vcc 对电容 C 充电,电路进入暂稳态 I,此后,电路周而复始地产生周期性的输出脉冲。多谐振荡器两个暂稳态的维持时间取决于 RC 充、放电回路的参数。暂稳态Ⅰ的维持时间,即输出 Vo 的正向脉冲宽度 T1≈0.7(R1+R 2)C; 暂稳态Ⅱ的维持时间,即输出 Vo 的负向脉冲宽度 T2≈0.7R 2C。 因此, 振荡周期 T=T 1+T 2=0.7(R 1+2R 2 )C,振荡频率 f=1/T 。正向脉冲宽度 T1 与振荡周期 T 之比称矩形波的 占空比D ,由上述条件可得 D=(R1+R2)/(R1+2R 2),若使 R2>>R 1,则 D≈1/2, 即输出信号的正负向脉冲宽度相等的矩形波(方波)。

仿真电路如下图1:

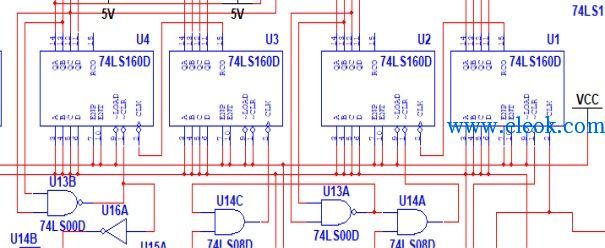

图1 3.2计时模块设计 (1)分、秒计时 在数字钟的控制电路中, 分和秒的控制都是一样的, 都是由一个十进制计数器和一个六进制计数器串联而成的,在电路的设计中我采用的是统一的器件 74LS160D的异步清零法来实现十进制功能和六进制功能, 根据 74LS160D的结构 把输出端的 0110(十进制为 6)用一个与非门 74LS00引到 CLR端便可置 0,这 样就实现了六进制计数。而74LS160D本身为计满后为10,与前文6进制串联后成60进制。 仿真电路如下图2所示:

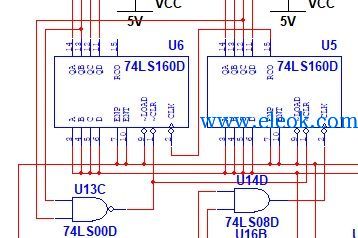

图2 (2)时计时器 由两片十进制同步加法计数器 74LS160 级联产生,采用的是异步清零法, u1输出端为 0001(十进制为 4)与 u2输出端 0010(十进制为2)经过与非门接 两片的清零端,从而实现了24进制计数。 仿真电路如下图3所示:

图3 3.3 译码显示模块设计 译码显示模块采用共阴极数码管及共阴七段数码管译码器驱动器CD4511构成。 CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,用于驱动共阴极 LED (数码管)显示器的 BCD 码-七段码译码器。具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动共阴LED数码管。 其功能表如下所示:

将计数器输出连接至译码器输入,再将译码器输出接入数码。 数码管本质为LED灯构成所以需要串联电阻进行分压,防止LED灯烧毁。 仿真图如下图4所示:

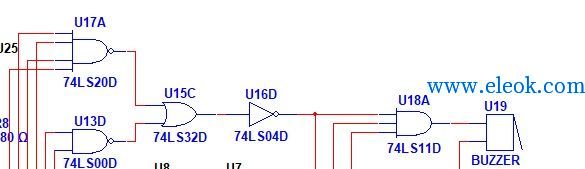

图4 3.4 整点报时模块设计 整点报时电路由门电路以及蜂鸣器构成。 由门电路判断整时,即判断59分50秒,即分计时为(0110)、(1001),秒计时为(0110)。以此判断整时,实现整时报时。 门电路由74LS20D四输入与非门判断(0110)、(1001),二输入与非门判断(0110)。 仿真电路如下图5所示:

图5 3.5校时模块设计 校时模块电路由复位按钮及二输入或门构成。 复位按钮上拉电阻,当分为按钮按下时,电阻接地,电平由高变低,实现手动产生脉冲。 将手动脉冲以及进位产生的脉冲分别输入二输入或门,或门输出进入计数器CLK端,则当按钮按下手动脉冲产生,计时器亦会进行计时,从而实现校时。 仿真电路如下图6所示:

图6

4 结论 通过对软件 Multisim 的学习和使用,进一步加深了对数字电路的认识。在仿真过程中遇到许多困难, 但通过自己的努力和同学的帮助都一一克服了。首先,连接电路图过程中,数码管不能显示, 后经图形放大后才发现是电路断路了。 其次布局的时候因元件比较多,整体布局比较困难,因子电路不如原电路直观, 最后在不断努力下,终于不用子电路布好整个电路。 调试时有的器件在理论上可行,但在实际运行中就无法看到效果,所以得换不少器件,有时无法找出错误便更换器件重新接线以使电路正常运行。在整个设计中,74LS160的接线比较困难,反复修改了多次,在认真学习其用法后采用归 零法和置数法设计出 60 进制和 24 进制的计数器。 同时,在最后仿真时,预置的频率一开始用的是 1hz,结果仿真结果反应很慢,后把频率加大, 这才在短时间内就能看到全部结果

【必读】版权免责声明

1、本主题所有言论和内容纯属会员个人意见,与本论坛立场无关。2、本站对所发内容真实性、客观性、可用性不做任何保证也不负任何责任,网友之间仅出于学习目的进行交流。3、对提供的数字内容不拥有任何权利,其版权归原著者拥有。请勿将该数字内容进行商业交易、转载等行为,该内容只为学习所提供,使用后发生的一切问题与本站无关。 4、本网站不保证本站提供的下载资源的准确性、安全性和完整性;同时本网站也不承担用户因使用这些下载资源对自己和他人造成任何形式的损失或伤害。 5、本网站所有软件和资料均为网友推荐收集整理而来,仅供学习用途使用,请务必下载后两小时内删除,禁止商用。6、如有侵犯你版权的,请及时联系我们(电子邮箱1370723259@qq.com)指出,本站将立即改正。

|