利用SystemView及Multisim设计了卷积码的编解码过程,并且有相关参数的测定,附件内有设计文档和仿真文件

完整资料(仿真文件、word文档):

卷积码设计.zip

(1.03 MB, 售价: 6 E币)

卷积码设计.zip

(1.03 MB, 售价: 6 E币)

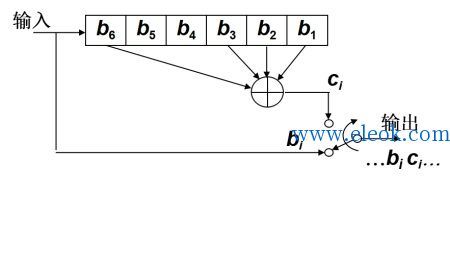

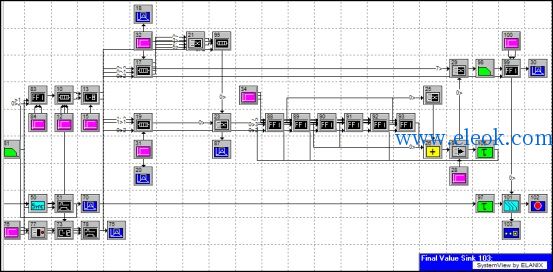

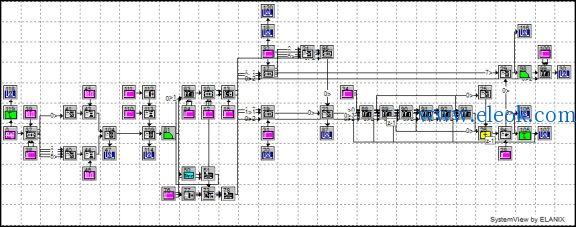

卷积码编译码器设计 (1)利用移位寄存器和异或器实现卷积码编码; (2)编码后信号送入高斯白噪声信道传输; (3)接收端进行大数逻辑解码译码; (4)要考虑实现位同步电路; (5)观察输出信号波形与输入信号波形的相关性,测量误码率曲线; (6)基于Systemview/Matlab/Simulink软件实现。 2 编码部分 2.1 编码原理 卷积码是一种非分组码,(2,1,6)卷积码信息位为1,监督位为1,监督位不仅与当前信息段有关还与前面5个信息段有约束关系。卷积码编码器由移位寄存器和异或器组成,原理框图如下。

图2.1 (2,1,6)卷积码编码原理框图 如图,信息位的b1,b2,b3,b6异或形成监督位,信息位与监督位交替输出。 2.2 编码仿真电路

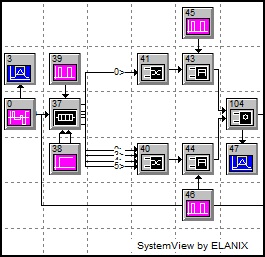

图2.2 编码部分仿真电路 上图为在system view中搭建的电路图,0号模块采用PN码作为信源,频率为10hz,码元长0.1s,信息位先存放在移位寄存器中,根据移位寄存器的结构与编码原理图对照,移位寄存器的0,3,4,5管脚异或作为监督位,42,43,44,45,46号模块相当于原理框图中的开关,45,46模块为周期10hz的脉冲,一个周期中高低电平各占0.05s,而46模块相位延迟180,假设45模块输出高电平和信息位相与,输出取决于信息位,此时46号模块为低电平,44号模块输出为0,也就是信息位输出时,监督位为0,监督位输出时,信息位为0。 3 位同步

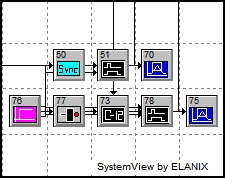

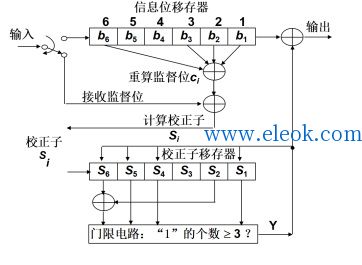

图3.1 位同步仿真电路 信源经过编码后,码元长度变为0.05s,频率增加了一倍,变成20hz,50号模块为system view的位同步模块,设置好参数可以直接输出位同步信号,51号模块为单稳态多谐振荡器,用于保持同步信号的高电平的时间,同时同步信号经过分频器,作为分离信息位与监督位等后续电路的时钟。 4 译码部分 4.1 译码原理 采用大数逻辑译码,先将信息位与监督位分离,信息位存放在移位寄存器中,按照编码的方式重新计算监督位,重新计算的监督位与接收的监督位异或,形成矫正子,若没有误码,重新计算的监督位与接收的监督位相同,矫正子为0,若存在误码则矫正子为1,通过矫正子纠正误码。

图4.1 (2,1,6)卷积码译码原理框图 上图为(2,1,6)的译码原理框图,信息位暂存于移位寄存器,重新计算监督位,与接收到的监督位异或运算后形成矫正子,矫正子存于移位寄存器中。大数逻辑解码用正交校验方程组判断信息位的对错,原理如下: S1 = c1 + b1 S2 = c2 + b2 S3 = c3 + b3 S4 = c4 + b1 + b4 S5 = c5 + b1 + b2 + b5 S6 = c6 + b1 + b2 + b3 + b6 监督关系式经过线性变换后形成正交校验方程组。 S1 = c1 + b1 S4 = c4 + b1 + b4 S5 = c5 + b1 + b2 + b5 S6+S2 = c2 + c6 + b1 + b3 + b6 此时信息位b1同时存在于上面4个式子中,若b1出现误码,则S1,S4,S5,S6+S2都为1,若不是b1发生误码而是其他码元发生误码,则S1,S4,S5,S6+S2仅有一个为1,从而精确判断该位信息位是否发生误码,若改码发生误码门限电路输出高电平,与信息位异或,使其取反,从而纠正错码,同时利用检测信号将矫正子清零。 4.2 译码仿真电路

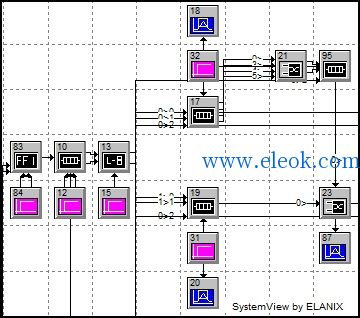

图4.2 译码部分仿真电路 经过信道传输和滤波器后,首先抽样判决,通过移位寄存器于锁存器分离信息位与监督位,信息位用异或器重新计算监督位,再与接收到的监督位异或形成矫正子,95号模块移存器用于码元的对正。

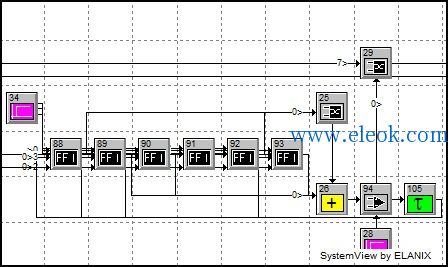

图4.3 译码部分仿真电路 矫正子存放于由D触发器组成的移位寄存器,方便监测信号反馈清零。按照原理框图,S6与S2异或后和S1,S4,S5相加,通过94号模块比较器和28号门限电平3比较,若相加大于等于3,比较器正向输出口输出高电平,使信息位取反,同时比较器的反向输出口延迟一位码元输出低电平使移存器清零,这部分电路要求码元严格对正,否则无法纠正错码还会增加新的错码。

图4.4 译码部分总电路 5 误码率仿真

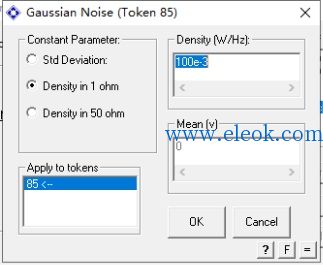

图5.1 信道部分仿真电路 信道中叠加高斯白噪声,96号模块增益设置全局变量使噪声信号的功率随loop增加而减小。高斯噪声以及全局变量的设置如下图。

图5.2 高斯噪声设置

图5.3 全局变量设置

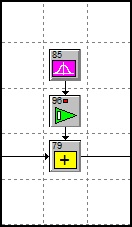

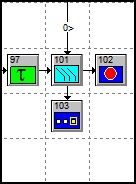

图5.4 误码率监测电路 通过97号模块延迟器,将信源与输出码元对正,送入101比特误码率模块观测误码率。

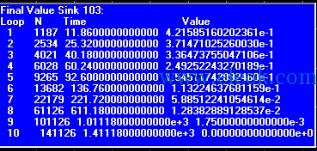

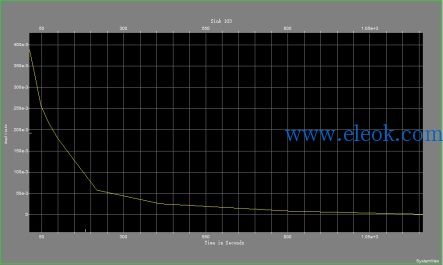

图5.5 误码率 误码率可以看出,随着loop的增加,噪声的减小,误码率呈下降趋势。103号模块同时可以描绘出误码率曲线,如下图。

图5.6 误码率曲线

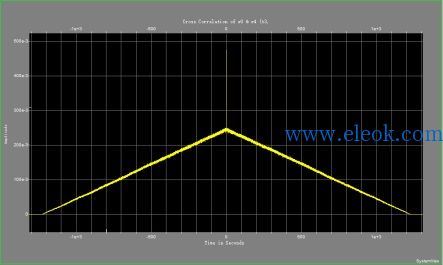

图5.7 输出与输入互相关函数 由相关图像可知,信源与输出是相关的。 6 纠正一位错码仿真

图6.1 纠错仿真电路总图

图6.2 人为添加信道脉冲 与观测误码率不同,信道中不再叠加高斯噪声。110号阶跃模块起始时间为1s,111号阶跃模块起始时间为1.05s经过反相器后与110号阶跃相与,可以人为在1s处加入码元宽度的脉冲,造成误码。

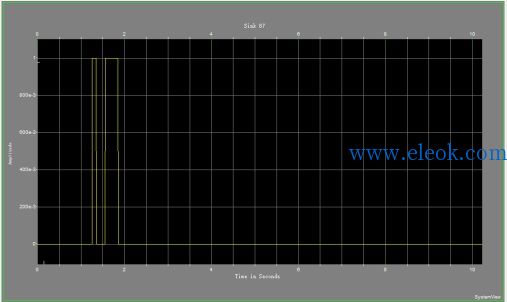

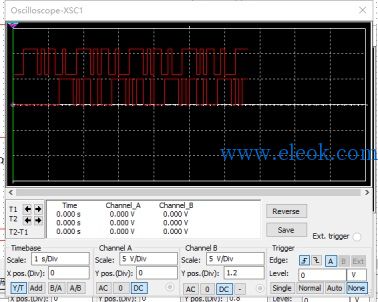

图6.3 矫正子波形 上图为87号模块示波器观测的矫正子波形,这说明加入的脉冲此时确实产生了误码。

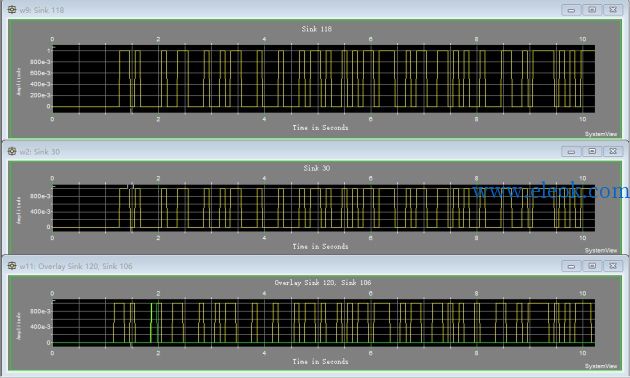

图6.4 对比观测图 最上方为118号模块示波器观测的波形,是信源延时后观测的波形,中间为116号示波器观测的译码完成后的波形,对比观测上方和中间两幅图可以看到输出和信源一样,这一位误码被纠正了。最下面黄色的波形为120号示波器观测的接收后的信息位,绿色的波形为106示波器观测的矫正子相加比较经过门限电路的输出,同时对比信源的波形可以看到,信息位有一位的误码,这一位误码被门限电路的输出纠正过来了。 7 电路级仿真 采用Multisim进行仿真,信源采用4级线性反馈移位寄存器生成的15位m序列,电路如下图。

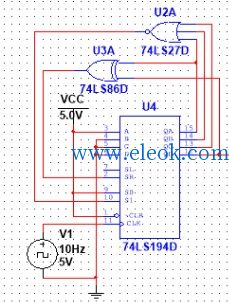

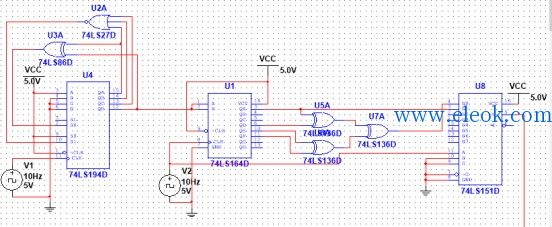

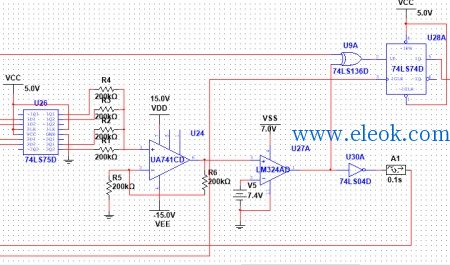

图7.1 信源生成电路 根据原理框图和system view的仿真电路搭建编码仿真电路,系统级仿真电路里,信息位与监督位二合一的部分实现比较麻烦,采用数据选择器并入串出,实现该功能,如下图。

图7.2 编码仿真电路

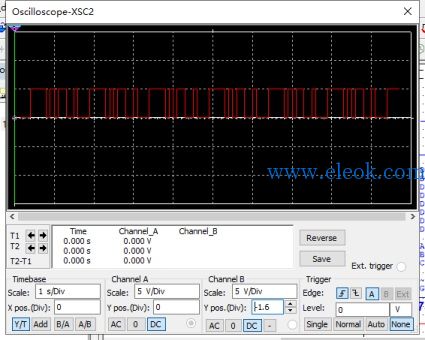

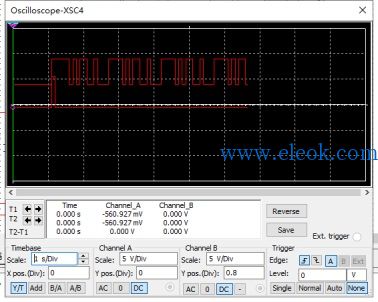

图7.3 信源波形

图7.4 编码后波形 编码时,信源先经过一次移位寄存器,所以最前面m序列多出一个0,为了方便分析,只选取前几位,观察波形可知,信源为0000111101011001,编码后波形为00000000111111100010011111010011,经过计算后,符合原理规律。

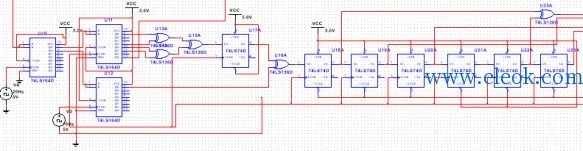

图7.5 译码部分电路 根据原理框图和system view已做好的电路,前面的译码部分电路可以直接使用,而system view中的加法器和比较器可以用运算放大器实现,如下图。

图7.6 相加电路与门限电路 加法运算之前,通过锁存器对波形进行抽样整形,1信号为5伏,0信号为0伏,加法电路由ua741构成,比较电路由lm324构成,根据同向加法器的原理的计算,每加一个1,输出上升2.5伏,当S1,S4,S5,S6+S2相加超过3时,输出大于7.5伏,门限值选择7.4伏略低于7.5伏,这部分电路单独仿真验证过,符合预期计算。

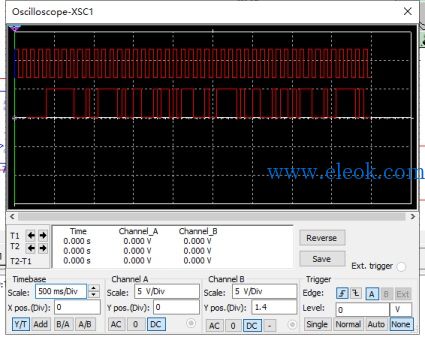

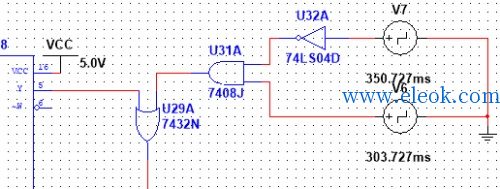

图7.7 信道人为添加脉冲 与之前的验证相同,在信道中人为添加脉冲,使其在信息位中产生误码,信源由最初的0000111101011001变为0001111101011001。

图7.8 译码分离的信息位与门限电路输出对比图 由上图可以观察到,门限电路输出的高电平正好对应误码位置,由此纠正误码。

图7.9 信源与译码对比图 根据信源与译码对比观察,译码后波形与信源相同,误码得以纠正。 8 总结与体会 纸上得来终觉浅,学习过理论课后仅仅了解了卷积码的工作原理,自己动手实践才发现有很多细节需要注意。在门限电路的输出不仅可以纠正一位误码,还用于矫正子的清零,而一开始注意到延迟就将比较器反向输出的信号送入触发器的清零端,导致其输出不是矩形波而是三角波;做译码部分的时候,没有注意到码元的严格对正,无法验证纠正一位误码。亲自动手实践后,对卷积码的理论有了更加深刻的理解和认识。

【必读】版权免责声明

1、本主题所有言论和内容纯属会员个人意见,与本论坛立场无关。2、本站对所发内容真实性、客观性、可用性不做任何保证也不负任何责任,网友之间仅出于学习目的进行交流。3、对提供的数字内容不拥有任何权利,其版权归原著者拥有。请勿将该数字内容进行商业交易、转载等行为,该内容只为学习所提供,使用后发生的一切问题与本站无关。 4、本网站不保证本站提供的下载资源的准确性、安全性和完整性;同时本网站也不承担用户因使用这些下载资源对自己和他人造成任何形式的损失或伤害。 5、本网站所有软件和资料均为网友推荐收集整理而来,仅供学习用途使用,请务必下载后两小时内删除,禁止商用。6、如有侵犯你版权的,请及时联系我们(电子邮箱1370723259@qq.com)指出,本站将立即改正。

|